AMD EPYC Venice: 192 ядра Zen 6 и поддержка DDR5-8000

Содержание

Не знаете, какой ПК взять?

Ответьте на несколько вопросов — получите готовую сборку с ценой.

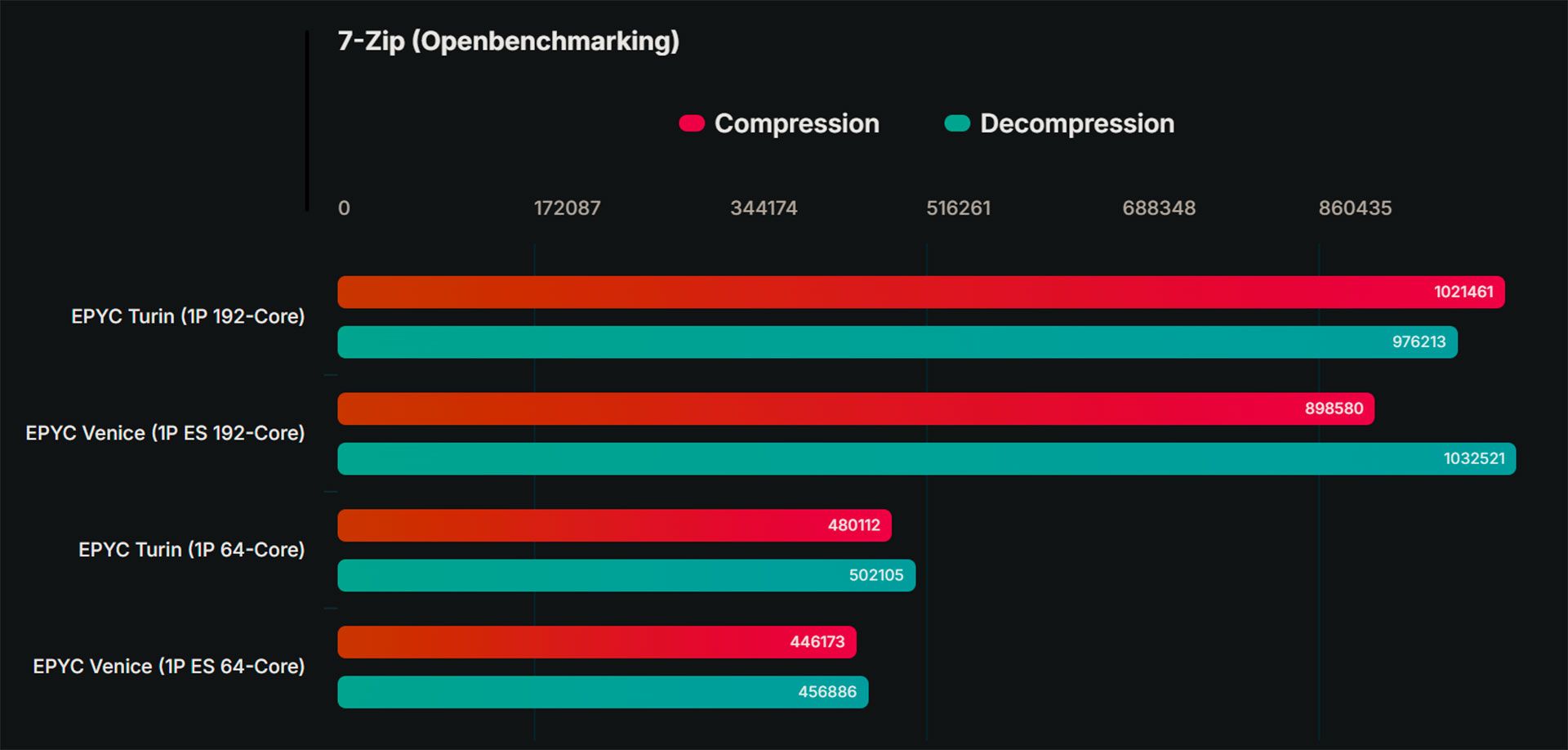

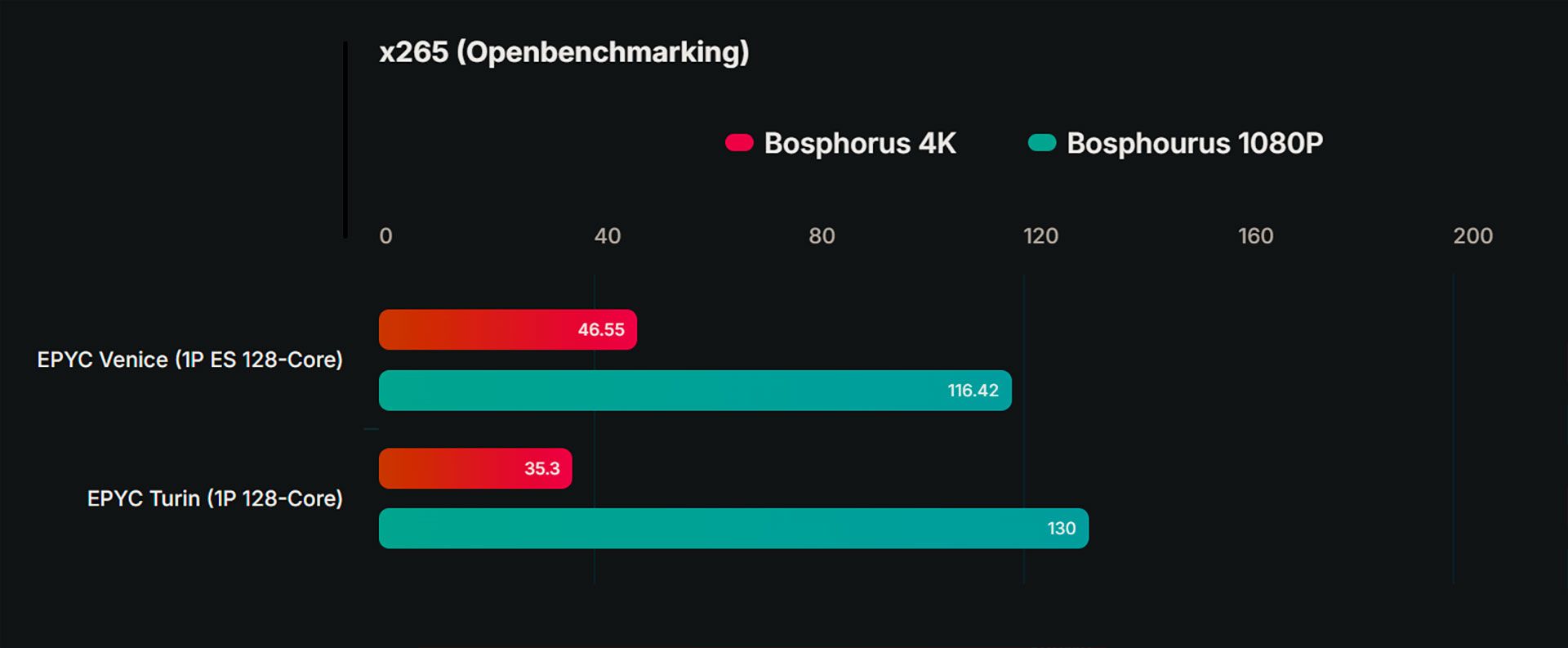

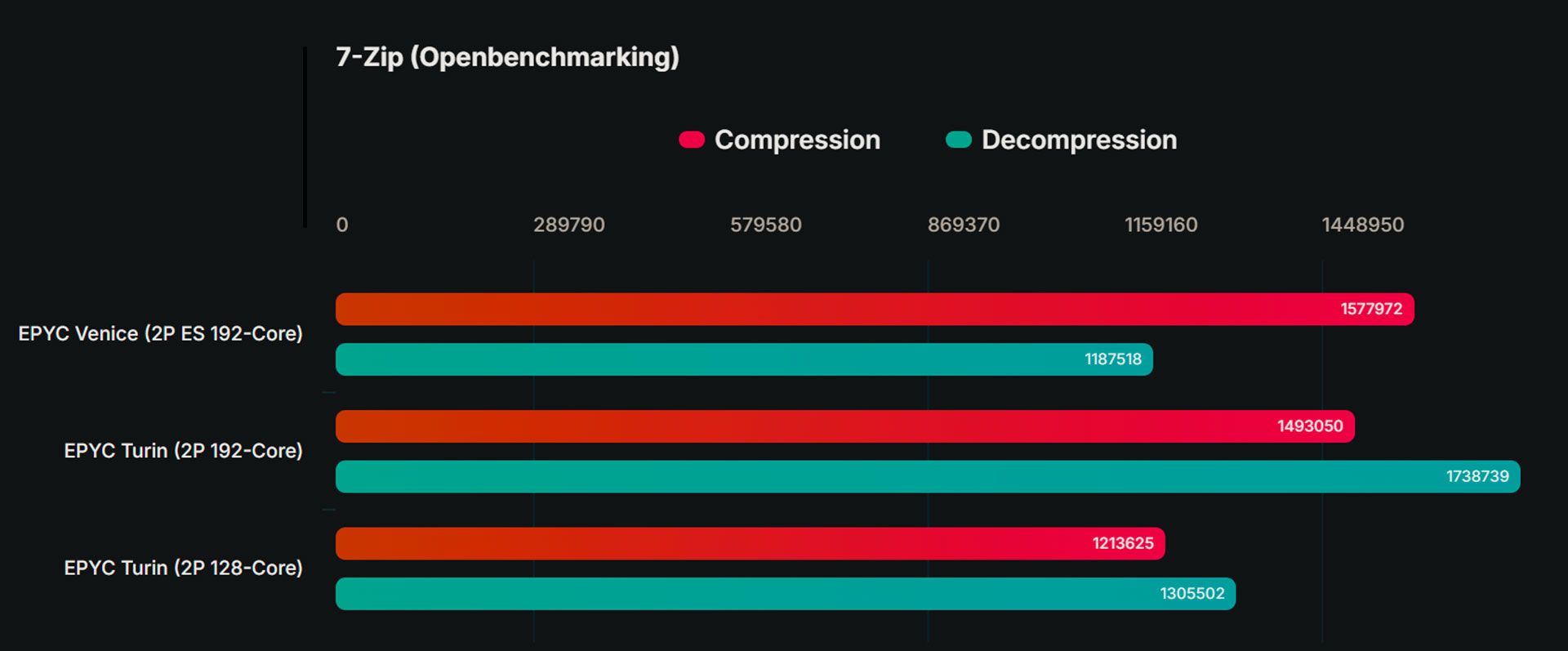

В базе данных OpenBenchmarking появились сведения об инженерных образцах серверных процессоров AMD следующего поколения под кодовым названием Venice. Чипы 6-й генерации EPYC строятся на базе микроархитектуры Zen 6 и демонстрируют впечатляющие количественные характеристики. Согласно утечкам, старшие модели располагают 192 физическими ядрами, а тестовые платформы уже поддерживают работу с высокоскоростной памятью.

Краткое содержание

- Инженерные образцы EPYC Venice получили от 64 до 192 ядер Zen 6;

- Тестовые платформы подтвердили поддержку оперативной памяти DDR5-8000;

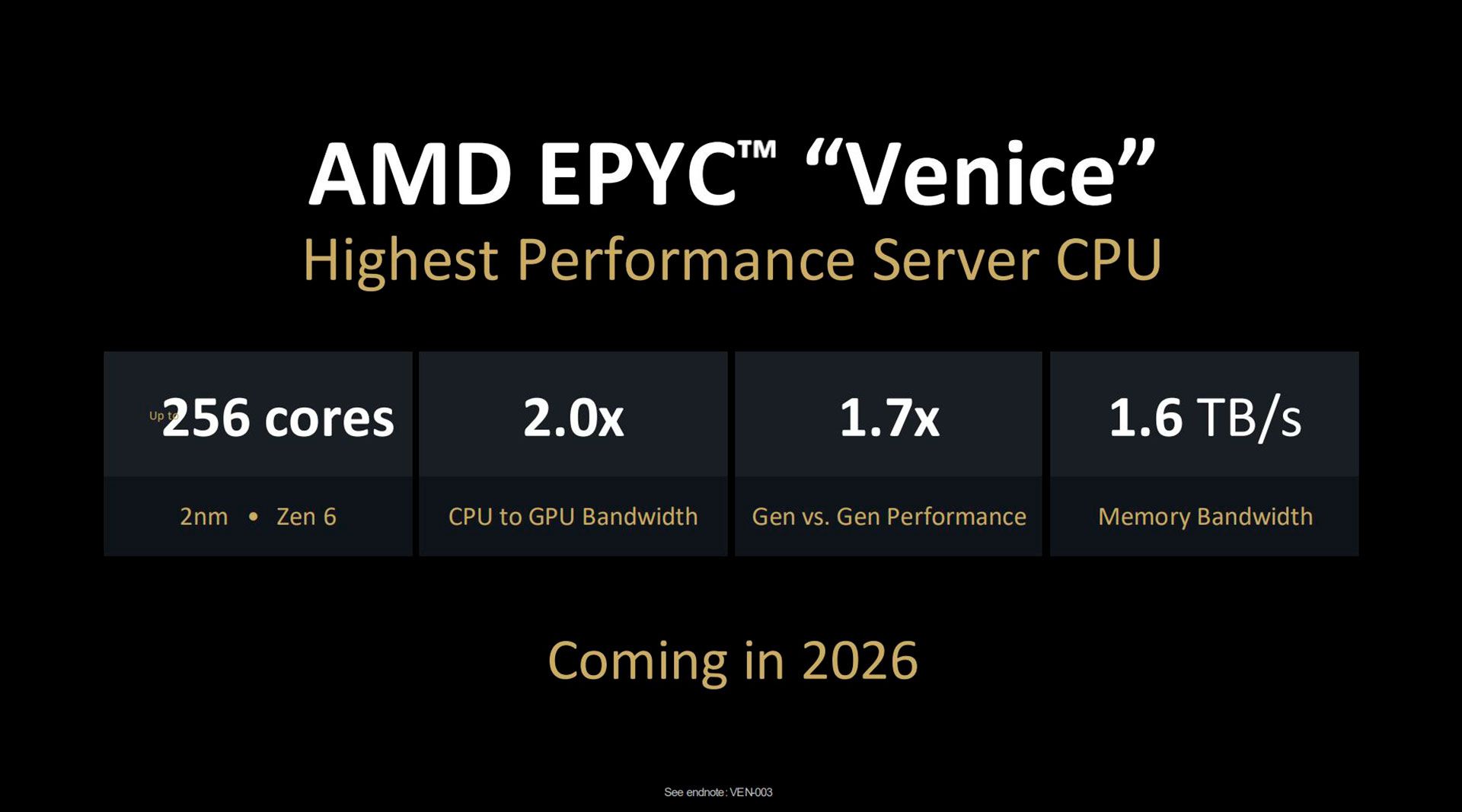

- Новое поколение чипов производится по передовому техпроцессу TSMC N2;

- Максимальное число ядер в готовых решениях может достичь 256 единиц;

- Официальный релиз серверной платформы намечен на 2026 год;

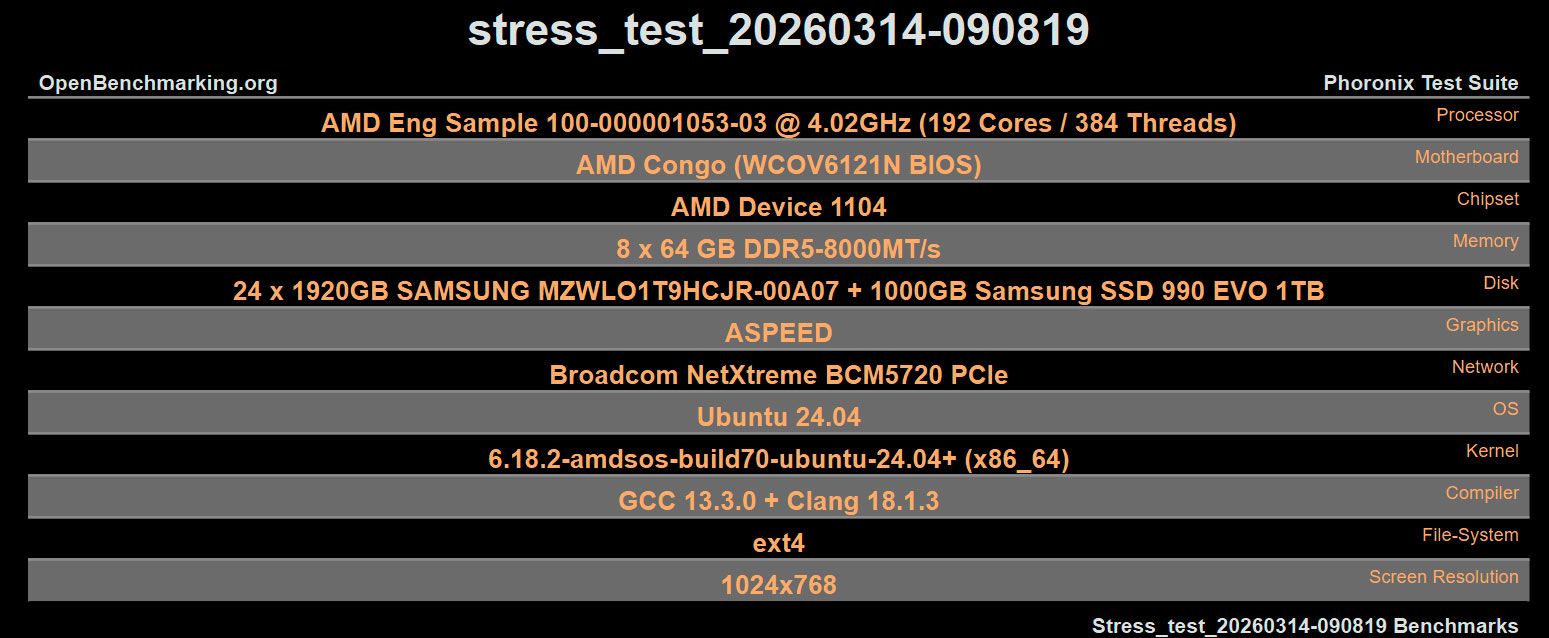

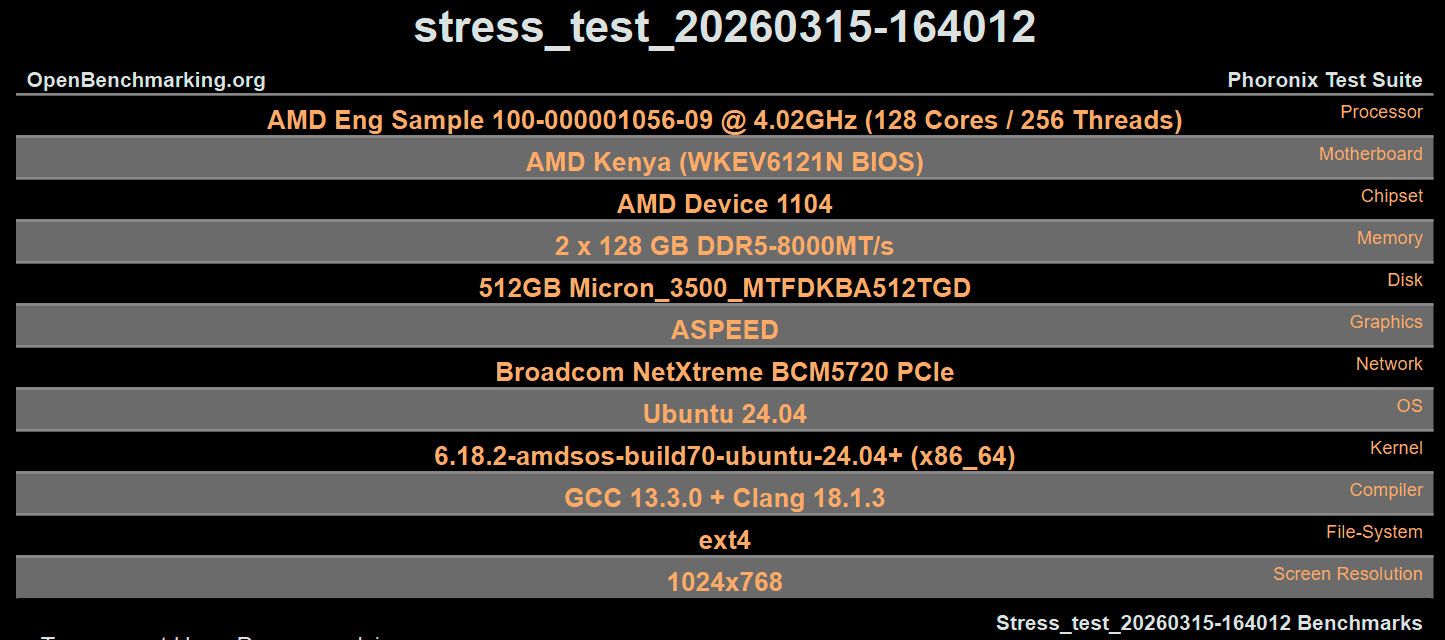

Платформы Congo, Kenya и Nigeria

Утечка раскрыла названия сразу нескольких инженерных платформ, названных в честь африканских стран и регионов. Система Congo была протестирована со 192-ядерным процессором и восемью модулями памяти DDR5-8000 по 64 ГБ каждый. Платформа Kenya использовалась для проверки 128-ядерного чипа с двумя планками памяти того же стандарта объёмом по 128 ГБ.

Также в базе засветилась двухсокетная система Nigeria. Она объединила два 64-ядерных образца, которые также работали с памятью DDR5-8000. Стоит отметить, что часть тестов проводилась с более медленной памятью DDR5-6400. Это указывает на ранний этап отладки оборудования, когда финальные спецификации ещё не утверждены окончательно.

Сейчас успели «засветиться» такие образцы CPU Zen 6:

- 100−000001053−03: 192 ядра/384 потока;

- 100−000001051−08: 192 ядра/384 потока;

- 100−000001056−09: 128 ядер/256 потоков;

- 100−000001056−03: 128 ядер/256 потоков;

- 100−000001863−02: 64 ядра/128 потоков;

- 100−000002138−02: 64 ядра/128 потоков.

Техпроцесс N2 и пропускная способность

AMD официально подтвердила, что архитектура Venice станет первым продуктом компании для высокопроизводительных вычислений (HPC), созданным на базе 2-нм техпроцесса от TSMC. Переход на более тонкие нормы литографии позволяет существенно нарастить плотность транзисторов и энергоэффективность. Ранее компания уже успешно захватила 40 процентов выручки серверного рынка, и новые решения призваны закрепить это доминирование.

Для обеспечения работы такого количества ядер требуется колоссальная пропускная способность памяти. Платформа Helios, в рамках которой будут выпускаться новые EPYC, предполагает поддержку до 256 ядер на сокет. При этом суммарная пропускная способность подсистемы памяти может достичь 1,6 ТБ/с. Для подобных вычислительных нагрузок требуются специализированные решения, такие как GPU-серверы для искусственного интеллекта, способные обрабатывать огромные массивы данных в реальном времени.

Перспективы рынка серверных решений

Разработка Venice ведётся в тесном сотрудничестве с Samsung. Компании совместно работают над оптимизацией высокопроизводительной памяти DDR5 для нужд дата-центров. Ожидается, что полноценный релиз 6-го поколения EPYC состоится в 2026 году. Появление столь мощных чипов критически важно для индустрии на фоне прогнозов о том, что в текущем году ЦОД потребят до 70 процентов всего мирового производства памяти.

Рост производительности серверных систем напрямую влияет на скорость обучения и работы нейросетей. Те, кто планирует развёртывание локальных вычислительных мощностей для профессиональных задач, могут изучить подборку серверов для машинного обучения. Это поможет заранее оценить требования к инфраструктуре перед выходом новых поколений «железа».

Не пропусти главное в мире ПК

Мы публикуем последние новости из компьютерного мира. Подписывайся, чтобы быть в курсе и ничего не пропустить.